The wave of Artificial Intelligence (AI) is turning the gears of a new cycle in the global semiconductor industry, with the key technology of AI-accelerated chip advanced packaging being pushed to a new vantage point. Major manufacturers such as TSMC, ASE, Amkor, Intel, and Samsung are actively betting and adjusting their production capacity layouts, with acquisitions of large and small enterprises, and subsidies and rewards from various countries in place... The advanced packaging market is bustling, and the news that the CoWoS production capacity is still "tight" has once again attracted the attention of the industry.

I. Is there a "big shortage" in CoWoS production capacity, and is Foveros expected to fill in?

The CoWoS packaging technology has long been regarded as the key to the production of cutting-edge AI chips. With the surge in AI demand, TSMC's CoWoS production capacity is in short supply. It is worth noting that recently, the industry has heard that due to the persistent demand for TSMC's advanced packaging CoWoS production capacity, Nvidia has approached Intel for advanced packaging. Supply chain manufacturers have pointed out that TSMC's CoWoS-S and Intel's Foveros packaging technologies are similar, and the latter can quickly provide packaging production capacity.

Advertisement

Looking at the usage of chip suppliers, Nvidia's A100, A800, A30, H100, H800, GH200 and other AI chips all rely on TSMC's CoWoS-S packaging technology and the process based on the 65nm silicon interposer; peer AMD's MI300 has also introduced CoWoS technology; MediaTek and TSMC cooperate, intending to use CoWoS for its ASIC chips; Broadcom's ASIC will also adopt CoWoS-L... More and more companies favor CoWoS, and industry insiders believe that TSMC's CoWoS production capacity is the main reason for the current AI chip shipment bottleneck.

According to TrendForce's survey, in terms of Nvidia's B100, its chip size will double that of the H100, consuming more CoWoS usage. It is estimated that by 2025, the main supplier TSMC's CoWoS production capacity will reach a total capacity of 550k-600k by the end of the year, with a growth rate approaching 80%.NVIDIA plans to launch the B100 and B200 in the second half of 2024, targeting CSP (Cloud Service Provider) customers, and is also planning a downgraded version, the B200A, for other enterprise customers, aiming at edge AI (Artificial Intelligence) applications. According to the latest survey by TrendForce, influenced by the tight capacity of CoWoS-L packaging, NVIDIA will provide the production capacity of B100 and B200 to CSP customers with greater demand and plans to supply them gradually after the third quarter of 2024. With the yield and mass production of CoWoS-L still to be prepared, NVIDIA is also planning the downgraded version B200A for other enterprise customers and has switched to using CoWoS-S packaging technology.

Regarding capacity expansion, TSMC President C.C. Wei once stated at the second quarter legal meeting that the demand for CoWoS is almost doubling, and the company is actively expanding its capacity, hoping to achieve a supply-demand balance by 2025-2026. Currently, all of TSMC's CoWoS production capacity is in the Taiwan region. In addition, Reuters previously cited sources as saying that TSMC is considering establishing advanced packaging capabilities in Japan, one of which is to bring CoWoS packaging technology to Japan.

In December last year, TSMC's CoWoS monthly production capacity increased to 14,000 to 15,000 wafers; it is estimated that by the fourth quarter of 2024, TSMC's CoWoS monthly production capacity will be significantly expanded to 33,000 to 35,000 wafers; by the end of 2025, it will be further increased to 44,000 wafers per month.

TSMC's CoWoS advanced packaging plants are mainly distributed in Taoyuan Longtan (expanding CoWoS), Hsinchu Hsinchu Science Park, Miaoli Zhunan, Miaoli Tongluo, Taichung Central Science Park, Chiayi Chiayi Science Park, Tainan Southern Science Park (receiving Longtan InFO capacity allocation) in the Taiwan region. Among them, TSMC is building two CoWoS advanced packaging plants in the Chiayi Science Park. The first plant, P1, started construction in May, but suspected ruins were found, and construction of P1 has been temporarily suspended, while the second CoWoS plant (P2) project has been initiated.

On the Intel side, in January of this year, Intel announced that the 3D Foveros advanced packaging technology has begun mass production at Fab 9 in New Mexico, USA.From the perspective of Intel's advanced packaging layout, in addition to its research and development and production capacity in Oregon, USA, including New Mexico and the future Penang, Malaysia factory, the 3D advanced packaging capacity of the three bases will be increased by four times by 2025, but the capacity of the factory area has not been disclosed.

And Intel will have six factories in Malaysia in the future. The existing four are two packaging and testing factories in Penang and Kulim, as well as the System Integration and Manufacturing Services Factory (SIMS) and the Self-Made Equipment Factory (KMDSDP) in Kulim, which are responsible for producing testing equipment; the ones under construction are packaging and testing factories and assembly testing factories in Penang and Kulim respectively. Among them, the packaging and testing factory in Penang will produce the most advanced 3D IC packaging Foveros in the future, which is expected to be put into use in 2024 or 2025.

II. Two protagonists: CoWoS VS Foveros

1. What is the special feature of CoWoS?

CoWoS, the full name in English is Chip-on-Wafer-on-Substrate, is a 2.5D, 3D packaging technology, which refers to the different functional modules made into small chips (chiplet), all sealed in a chip. Therefore, a chip contains logic chips, memory chips, RF chips, and micro-electromechanical chips, but this technology only serves the process below 7nm.CoWoS can be understood by dividing it into "CoW" and "WoS". "CoW" stands for "Chip-on-Wafer", which means chip stacking; "WoS" stands for "Wafer-on-Substrate", which is the process of stacking chips on a substrate. In layman's terms, CoWoS refers to the process of stacking chips and encapsulating them on a substrate to reduce the space required by the chips, enhance their performance, and simultaneously reduce power consumption and costs. It is applicable to fields such as high-performance computing (HPC), AI (Artificial Intelligence), data centers, 5G, the Internet of Things (IoT), and automotive electronics.

CoWoS is positioned in the downstream phase of the semiconductor industry chain, specifically in IC packaging and testing. The CoWoS technology currently used in the market is divided into three categories: CoWoS-S, CoWoS-R, and CoWoS-L.

CoWoS-S utilizes a single-chip silicon interposer and through-silicon vias (TSV) to facilitate the direct transmission of high-speed electrical signals between the chip and the substrate. It is important to note that the single-chip silicon interposer contains yield issues. At present, the main technologies of Amkor and Intel are still CoWoS-S, focusing on Nvidia's H series of chips.

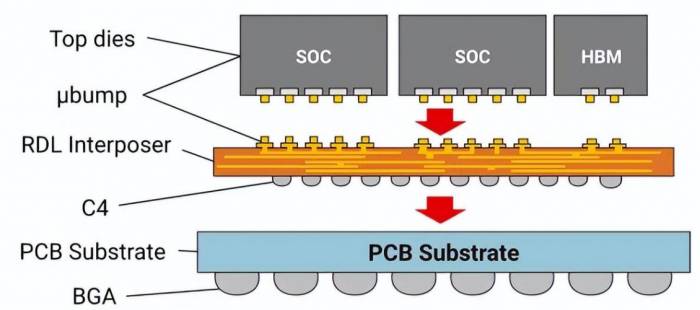

The CoWoS-R series adopts the InFO technology, with the redistribution layer (RDL) acting as an interconnect between chips, especially in the heterogeneous integration of HBM (High Bandwidth Memory) and SoC (System on Chip). The RDL interposer is composed of polymers and copper wires, offering relative mechanical flexibility. This flexibility enhances the integrity of the C4 (Controlled Collapse Chip Connection) joints and allows the new packaging to expand its size to meet more complex functional requirements.

CoWoS-L combines the advantages of CoWoS-S and InFO technology, using an interposer with LSI (Local Silicon Interconnect) chips for inter-chip interconnection, and an RDL layer for power and signal transmission, thus providing the most flexible integration. This product starts from a 1.5X reticle interposer size, including 1xSoC + 4xHBM cubes, and further expands the packaging to a larger size to integrate more chips.The CoWoS-L technology mitigates the yield issues caused by the use of large silicon interposers in CoWoS-S. The industry has stated that in some implementation schemes, this technology can also use Through-Insulator Vias (TIV) to replace TSVs, to minimize insertion loss.

As chip miniaturization continues, chip costs are also increasing. With the support of CoWoS technology, packaging chips of different processes together can achieve accelerated computation and controllable costs. For this reason, the industry believes that the emergence of CoWoS technology has extended the life of Moore's Law. However, this technology still faces issues such as thermal equilibrium and yield improvement after chip stacking.

In addition, the InFO technology mentioned here refers to the use of semiconductor process technology during the stacking process, which reduces the use of intermediate wire carrier boards, greatly reducing packaging costs. It can also achieve a thinner and lighter size, which is beneficial for heat dissipation and reducing chip power consumption.

2. Foveros: Industry's First 3D IC

Foveros is a Greek word meaning "unique, special." This technology is a high-performance three-dimensional integrated circuit (3D IC) face-to-face stacking packaging technology invented by Intel, which was introduced in 2019.The Foveros technology is designed to integrate two or more chips together, with interconnections between the horizontal and vertical directions, further reducing the bump pitch. However, the 3D stacking of logic chips in Foveros is not a single chip, but a logic wafer 3D stacking technology, which stacks chiplets or dies face to face. This technology, through clever design, can significantly improve the latency and bandwidth of certain components by stacking memory on top of active components. Products can be divided into smaller chiplets or tiles, where I/O, SRAM, and power transfer circuits are manufactured in the base chip, and high-performance logic chiplets or tiles are stacked on top.

Foveros achieves extremely low power consumption and high-density chip-to-chip connections within the chip, minimizing the overhead of partitioning, allowing for the selection of rational chip processes for each block, and ensuring cost and performance improvements, simplifying the creation of SKUs (Stock Keeping Units), making them easier to customize and faster to market. Different technology versions include Foveros Omni and Foveros Direct.

Intel's first-generation Foveros is introduced using a 10nm process, with extremely low power consumption of 0.15 picojoules per bit, and a bandwidth that is 2-3 times that of similar 2.5D Si interposers, with power ranging from 3W to 1 kilowatt, and the bump pitch was 50 micrometers at the time.

Foveros Omni allows for chip separation, offering strong flexibility, and can mix multiple top chip blocks and multiple base blocks on hybrid chip nodes, providing performance 3D stack technology for chip-to-chip interconnects and modular design.

Foveros Direct, on the other hand, is a complement to Foveros Omni, supporting the direct connection of one or more chiplets to the underlying active base chip to create complex system modules. According to Intel, the "direct" connection is achieved by thermal compression of the copper wires of individual chiplets to the wafer, or by directly stacking the entire wafer to connect. This connection technology can be "face-to-face" or "back-to-back" and incorporates chips or wafers from different foundries, enhancing product architecture flexibility. The connection bandwidth is determined by the pitch of the copper wires (and the resulting density). The first generation of Foveros Direct 3D will use a 9-micron pitch to connect copper wires; the second generation will reduce the pitch to only 3 micrometers. This technology has achieved a collision pitch of less than 10 micrometers, increasing the interconnect density of 3D stacking and pioneering new concepts for functional chip partitioning that were previously unattainable.Foveros Direct 3D supports high bandwidth and low latency interconnects between stacked chips.

Intel has emphasized that as the entire semiconductor industry enters the heterogeneous era of integrating multiple small chips (Chiplets) in a single package, Intel's advanced packaging technologies such as 3D Foveros and 2.5D EMIB will be able to achieve the integration of one trillion transistors in a single package, in order to continue driving Moore's Law forward after 2030.

In addition, it is worth mentioning that Intel's EMIB 3.5D is a technology that embeds multi-chip interconnect bridges and Foveros technology in a single package, suitable for applications that require the combination of multiple 3D stacks in one package. Its Data Center GPU Max Series SoC, using EMIB 3.5D, has created the most complex heterogeneous chip ever mass-produced by Intel, with more than 100 billion transistors, 47 active magnetic tiles, and 5 process nodes.

Conclusion

The advanced packaging market has become a battleground for all. Currently, six major manufacturers, including ASE, Amkor, Jiangsu Changjiang Technology, TSMC, Samsung, and Intel, account for nearly 80% of the entire advanced packaging market share. Each company has a variety of chips in hand, among which TSMC's advanced packaging technologies include not only the aforementioned CoWoS-S, CoWoS-R, CoWoS-L, but also InFO-OS, InFO-LSI, InFO-SOW, InFO-SoIS, SoIC, FOPLP, etc.; Intel includes EMIB, Foveros, Foveros Omni, Foveros Direct, etc.; other major manufacturers, such as Samsung, have FOSiP, X-Cube, I-Cube, HBM, DDR/LPDDR DRAM, CIS, etc., and Jiangsu Changjiang Technology has covered SiP, WL-CSP, 2.5D, 3D, etc.Overall, in the post-Moore era, the rapid growth in demand for artificial intelligence (AI) and high-performance computing has significantly elevated the prosperity of the advanced packaging market compared to the overall packaging industry. The market is unprecedentedly booming, attracting many heroes to gather together, and the competition is becoming increasingly fierce. The prosperity of the advanced packaging market will also promote the upward development of the global semiconductor industry.

Comments